Scientific journal

Scientific Review. Technical science

ISSN 2500-0799

ПИ №ФС77-57440

MICROPROGRAM IMPLEMENTATION AND EXPERIMENTAL TEST OF THE TRAINING MICROPROCESSOR IN MICROSOFT EXCEL

Важную роль при изучении процессоров ЭВМ играют практические занятия и лабораторные работы, позволяющие обучающимся получить более глубокие знания. Для проведения лабораторных работ часто используются программные модели реальных [1, 2] или учебных [3, 4] процессоров. Программные модели могут быть кроссплатформенными, а также представлять собой веб-приложения. В программных моделях реальных процессоров обучаемым доступна архитектура процессора на уровне системы команд, поэтому экспериментальные исследования в основном связаны с разработкой и покомандным выполнением ассемблерных программ. Программные модели учебных процессоров могут быть ориентированы на микропрограммируемые процессоры и позволять обучающимся проводить самостоятельную разработку микропрограмм интерпретаторов команд и экспериментальное исследование процессоров с различной архитектурой [4, 5]. Такие модели дают возможность исследовать работу процессора не только на уровне архитектуры, но и на уровне «микроархитектуры», отражающей структуру процессора и демонстрирующей потактовое выполнение команд.

Цель исследования: развитие технологии применения функциональных моделей микропрограммируемых вычислительных структур в учебном процессе, использующей в качестве средства моделирования табличный процессор Microsoft Excel и позволяющей осуществлять микропрограммную реализацию и экспериментальное исследование учебного процессора ЭВМ.

Предлагается подход к микропрограммной реализации и экспериментальному исследованию учебного процессора ЭВМ, основанный на применении функциональной модели процессора с микропрограммируемой архитектурой в Microsoft Excel [5]. Моделируемый процессор с микропрограммируемой архитектурой называется далее базовым процессором (БПР), в отличие от учебного процессора (УПР), микропрограммная реализация которого осуществляется с помощью БПР.

Структура и возможности функциональной модели базового процессора

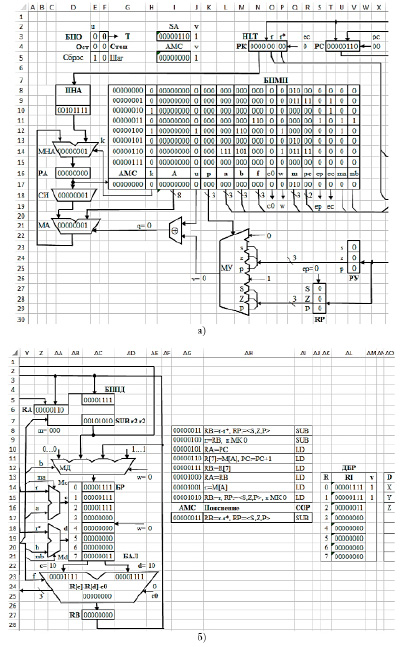

Используемая функциональная модель, кроме модели восьмиразрядного микропрограммируемого БПР, содержит модель оперативного запоминающего устройства. Структура БПР с запоминающим устройством отображается на экранной форме ПР-Ф при проведении экспериментальных исследований. На экранной форме ПР-Ф присутствуют следующие основные блоки (рис. 1) [5]: БПО – блок пуска-останова; БППД – блок памяти программ и данных; ПНА – преобразователь начального адреса, БПМП – блок памяти микропрограмм; БР – блок регистров; БАЛ – блок арифметико-логический.

Кроме того, в состав базового процессора входят (рис. 1): РК – регистр команд; PC – программный счетчик; RA – регистр адреса БППД, МНА – мультиплексор начального адреса, РА – регистр адреса, СИ – схема инкремента, МА – мультиплексор адреса, «⊕» – инвертор кода условия, МУ – мультиплексор условий и признаков, РУ – регистр условий, RP – регистр признаков, МД – мультиплексор данных, Mc, Md – мультиплексоры номеров регистров БР; RB – буферный регистр. На экранной форме ПР-Ф, используемой для проведения экспериментальных исследований (рис. 1), также отображаются: SA – пультовый регистр ввода в PC адреса команды; АМК – пультовый регистр ввода в RA – адреса микрокоманды; ДБР – пультовый дублер блока регистров.

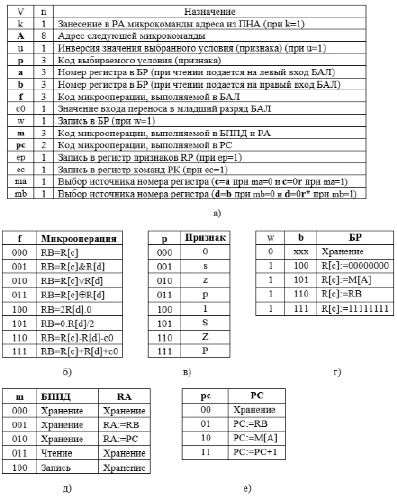

Основу операционной части базового процессора составляют БР и БАЛ. БР содержит восемь восьмиразрядных регистров. Содержимое любой пары регистров с помощью двух трехразрядных входов номеров регистров может быть выбрано и передано на входы БАЛ, в котором выполняется одна из восьми микроопераций и формируются значения трех логических условий. Управляющая часть БПР представляет собой устройство управления с программируемой логикой, в памяти которого хранятся двоичные коды микрокоманд. На рисунке 2 показаны назначение и значения кодов многоразрядных полей микрокоманды (где V – наименование, n – разрядность поля, а M[A] – содержимое ячейки памяти с адресом A).

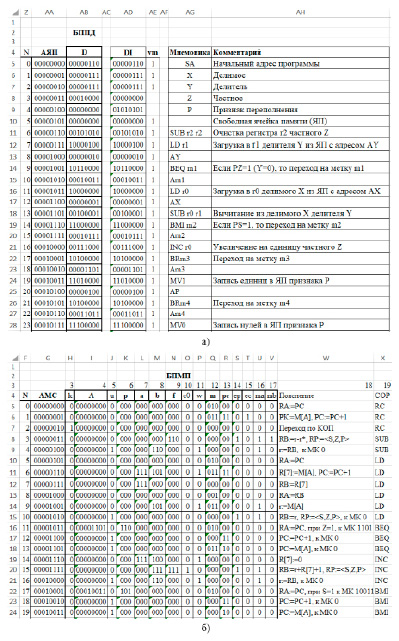

БПМП отображается на экранной форме проведения исследований ПР-Ф в виде блока памяти, в котором выделено окно микрокоманд, содержащее восемь последовательно расположенных 33-разрядных ячеек памяти (рис. 1а). Содержимое окна обновляется после выполнения каждой микрокоманды. Занесение данных в ПНА и БПМП производится на листе ПР-В путем ввода данных с клавиатуры в ячейки таблиц, моделирующих ПНА и БПМП, а также ячейки, предусмотренные для ввода дополнительной информации (пояснения, коды операций).

Работа БППД моделируется с помощью таблицы, расположенной на листе ПР-В. Ввод данных в БППД производится на экранной форме ПР-В аналогично записи в БР с помощью ячеек пультового дублера БППД. Данные вводятся с клавиатуры в выбранные дублирующие регистры БР (ячейки БППД), а соответствующие им управляющие сигналы v (vm) устанавливаются в единичное. При нажатии клавиши F9 данные из дублирующих регистров (ячеек), у которых v=1 (vm=1), переносятся в основные регистры БР (БППД).

Рис. 1. Экранная форма ПР-Ф: левая часть (а) и правая часть (б)

Рис. 2. Назначение полей микрокоманды (а) и значения кодов многоразрядных полей микрокоманды: БАЛ (б), БР (в), РС (г), БППД и RA (д), признаков (е)

Кроме того, по сигналу «Сброс» при единичном значении соответствующего управляющего сигнала (v) в PC (РА) может быть занесен предварительно набранный на клавиатуре стартовый адрес команды SA (адрес микрокоманды АМК).

Процессор функционирует под действием сигналов, вырабатываемых блоком пуска-останова БПО (рис. 1а), в состав которого входит генератор тактовых импульсов (ГТИ). В БПО с клавиатуры подаются сигналы «Сброс» (E5) и «Шаг» (F5) (в соответствующую ячейку MS Excel вводится необходимое значение сигнала (0 или 1) и нажимается клавиша F9). В БПО вырабатываются два признака: «Ост» и «Стоп». Признак «Ост» (останов) принимает единичное значение, если выполняется микрокоманда, содержащая микрооперацию останова (p=100), и нулевое значение – по сигналу «Сброс». Признак «Стоп» принимает единичное значение, если единичное значение имеет сигнал «Шаг» и выполняется микрокоманда, содержащая микрооперацию (k=1) перехода по коду операции, и нулевое значение – по сигналу «Сброс».

Проведению экспериментальных исследований предшествует изменение параметров Microsoft Excel, связанных с вычислением формул (выбираются вычисления в книге «вручную» и включаются итеративные вычисления с предельным числом итераций, превышающим удвоенное максимальное число микрокоманд, которые необходимо выполнить после нажатия клавиши F9). БПО обеспечивает работу БПР в следующих режимах: выполнение микрокоманды за два полутакта; выполнение микрокоманды за один такт; выполнение команды; выполнение программы.

Применение функциональной модели базового процессора в учебном процессе

Функциональная модель базового процессора позволяет производить микропрограммную реализацию и экспериментальное исследование учебных процессоров с различной архитектурой. В качестве исходных данных может выступать простая задача, на примере программного решения которой исследуется работа учебного процессора. Применение функциональной модели базового процессора позволяет обучающимся решать следующие проектные задачи для учебного процессора.

1. Разработка (выбор) алгоритма решения задачи.

2. Определение архитектуры процессора и программирование.

3. Кодирование программы и распределение памяти программ и данных.

4. Разработка микропрограммы командного цикла и составление таблиц прошивок ПНА и БПМП.

5. Ввод и отладка микропрограммы командного цикла и программы решения задачи.

Рассмотрим применение функциональной модели БПР в учебном процессе на примере операции деления нацело 8-разрядного двоичного числа X на 8-разрядное двоичное число Y.

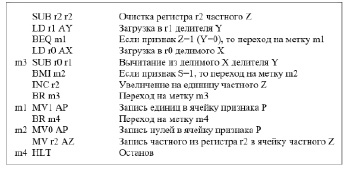

1. Разработка (выбор) алгоритма решения задачи. Для выполнения заданной операции предлагается использовать следующий алгоритм. Если число Y=0, то деление не выполняется, а формируется признак переполнения P. В противном случае из делимого X вычитается делитель Y, и если разность R положительное число, то частное Z увеличивается на единицу, а разность R выступает в качестве нового уменьшаемого на следующем шаге. Процесс вычитания продолжается до тех пор, пока не будет получена отрицательная разность. В этом случае Z будет представлять собой искомое частное от деления X на Y нацело [МПВУ].

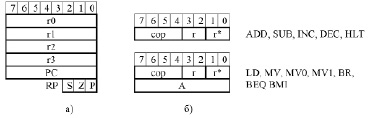

2. Определение архитектуры УПР и программирование. Определение архитектуры включает выбор программистской структуры (состава программно-доступных регистров) и определение внутреннего языка УПР (системы данных и системы команд). Программистская структура содержит: четыре общих регистра (r0–r3), программный счетчик (PC) и регистр признаков (RP), включающий три разряда: знака (S), нуля (Z) и переполнения (P) (рис. 3а).

Разработка системы команд предполагает определение набора операций, способов адресации, модификаций и форматов команд. Для рассматриваемого примера система команд УПР приведена в таблице 1, а форматы команд – на рисунке 3б. В таблице 1 использованы следующие обозначения: r,r*∈{r0,r1,r2,r3} – программно-доступные регистры: регистр r* является источником данных, а регистр r – приемником результата, но может также служить источником второго операнда; М[А] – ячейка памяти с адресом А; знак «+» в описании признаков означает, что устанавливается новое значение признака по результату выполнения команды, а знак «–» свидетельствует о сохранении старого значения признака.

Рис. 3. Регистры программистской структуры (а) и форматы команд (б)

Таблица 1

Система команд

|

Наименование |

Мнемоника |

Описание |

Признаки |

||

|

S |

Z |

P |

|||

|

СУММИРОВАНИЕ |

ADD r r* |

r:=r+r*, PC:=PC+1 |

+ |

+ |

+ |

|

ВЫЧИТАНИЕ |

SUB r r* |

r:=r-r*, PC:=PC+1 |

+ |

+ |

+ |

|

Инкремент |

INC r |

r:=r+1, PC:=PC+1 |

+ |

+ |

+ |

|

Декремент |

DEC r |

r:=r-1, PC:=PC+1 |

+ |

+ |

+ |

|

ЧТЕНИЕ В РЕГИСТР |

LD r A |

r:=M[A], PC:=PC+2 |

+ |

+ |

+ |

|

Запись ИЗ РЕГИСТРА |

MV r A |

M[A]:=r, PC:=PC+2 |

+ |

+ |

+ |

|

Запись НУЛЕЙ |

MV0 A |

M[A]:=00000000, PC:=PC+2 |

0 |

1 |

0 |

|

Запись ЕДИНИЦ |

MV1 A |

M[A]:=11111111, PC:=PC+2 |

1 |

0 |

0 |

|

ПЕРЕХОД |

BR A |

PC:=A |

– |

– |

|

|

ПЕРЕХОД, ЕСЛИ НУЛЬ |

BEQ A |

Если PZ=1, то PC:=A, иначе PC:=PC+2 |

– |

– |

|

|

ПЕРЕХОД, ЕСЛИ МИНУС |

BMI A |

Если PS=1, то PC:=A, иначе PC:=PC+2 |

– |

– |

– |

|

ОСТАНОВ |

HLT |

Останов |

– |

– |

– |

Рис. 4. Программа деления чисел нацело

Программа деления чисел нацело с использованием символики ассемблера, составленная в предположении, что исходные данные и результаты размещаются в блоке памяти программ и данных, приведена на рисунке 4.

3. Кодирование программы и распределение памяти программ и данных. Двоичные коды операций и начальные адреса их микропрограмм в блоке памяти микропрограмм приведены в таблице 2.

Ввод данных и команд в БППД производится с помощью экранной формы ввода ПР-В. Двоичные коды данных и команд для рассматриваемого примера занимают 28 ячеек памяти. Распределение памяти программ и данных для первых 23 ячеек показано на рисунке 5а.

Таблица 2

Коды операции и начальные адреса микропрограмм операций

|

Мнемоника |

Код операции |

Начальный адрес МП |

|

HLT |

0000 |

00101111 |

|

ADD |

0001 |

00101111 |

|

SUB |

0010 |

00000011 |

|

INC |

0011 |

00001110 |

|

DEC |

0100 |

00010100 |

|

LD |

1000 |

00000101 |

|

MV |

1001 |

00100111 |

|

BR |

1010 |

00010111 |

|

BEQ |

1011 |

00001011 |

|

BMI |

1100 |

00010001 |

|

MV1 |

1101 |

00011001 |

|

MV0 |

1110 |

00100000 |

Рис. 5. Экранная форма ввода ПР-В: область ввода данных и программ в БППД (а), область ввода микропрограмм в БПМП (б)

4. Разработка микропрограммы командного цикла и составление таблиц прошивок ПНА и БПМП. При разработке микропрограммы командного цикла (интерпретатора команд) производится распределение регистров УПР. В примере регистры программистской структуры r0–r3 занимают в блоке регистров регистры R[0]–R[3], программный счетчик и регистр признаков помещаются в одноименные регистры: PC и RP соответственно. Также в качестве вспомогательного, не являющегося регистром программистской структуры, используется регистр R[7] блока регистров. Микропрограмма командного цикла состоит из 48 микрокоманд. В первых трех ячейках БПМП находятся микрокоманды, которые обеспечивают: пересылку адреса команды из программного счетчика в регистр адреса БППД; чтение команды из БППД в регистр команд и увеличение содержимого программного счетчика на единицу; переход по коду операции к начальному адресу соответствующей микропрограммы (загрузку в РА из ПНА адреса первой микрокоманды микропрограммы выбранной операции). В остальных 45 ячейках размещаются микропрограммы 12 операций в соответствии с системой команд УПР. Ввод микропрограмм в БПМП производится с помощью экранной формы ввода ПР-В. Двоичные коды микрокоманд для рассматриваемого примера для первых 20 ячеек показаны на рисунке 5б.

5. Ввод и отладка микропрограммы командного цикла и программы решения задачи. Ввод данных осуществляется с помощью экранной формы ввода ПР-В. Для каждой операции в ячейку памяти ПНА, адрес которой совпадает с кодом операции, с клавиатуры заносится двоичный код начального адреса микропрограммы этой операции. В экранной форме ПР-В слева от каждой ячейки ПНА предусмотрено дополнительное поле для ввода мнемонического обозначения введенного кода операции. Это мнемоническое обозначение отображается на экранной форме исследования ПР-Ф над регистром команд при загрузке в него команды с данным кодом операции.

Микропрограмма командного цикла вводится в БПМП путем занесения с клавиатуры двоичных кодов микрокоманд. В экранной форме ПР-В справа от каждой ячейки БПМП предусмотрены два вспомогательных поля: «Пояснение» (для ввода описания выполняемых в микрокоманде микроопераций) и «COP» (для ввода мнемонического обозначения подмикропрограммы, к которой относится данная микрокоманда).

Отладка микропрограммы командного цикла осуществляется с помощью экранной формы исследования ПР-Ф в режимах выполнения микрокоманд по полутактам и тактам. Для упрощения отладки на экранной форме ПР-Ф при выполнении микрокоманд отображается следующая дополнительная информация: источник адреса при занесении адреса в регистр адреса БППД (RA:=PC или RA:=RB); двоичный код данного, поступающий с выбранного входа мультиплексора данных для записи в БР; двоичные коды номеров регистров и находящихся там данных, поступающие на входы БАЛ для выполнения микрооперации; символическое обозначение выполняемой в БАЛ микрооперации; содержание вспомогательных полей микрокоманд («Пояснение» и «COP») в продолжении окна микрокоманд. Кроме того, значения управляющих сигналов из микрокоманды дублируются на управляющих входах узлов и блоков, на которые они подаются. В процессе отладки микропрограммы командного цикла осуществляется выполнение необходимых последовательностей микрокоманд путем занесения в регистр адреса БПМП начального адреса первой микрокоманды, который предварительно вводится с клавиатуры в поле АМК. Перед выполнением любой микрокоманды также возможно изменение содержимого выбранных регистров в БР с помощью пультового дублера БР.

Ввод двоичных кодов команд и исходных данных программы в БППД производится в форме ввода ПР-В с помощью ячеек пультового дублера БППД. Команда может занимать одну или две ячейки БППД. В экранной форме ПР-В справа от каждой ячейки БППД предусмотрены два вспомогательных поля: «Мнемоника» (для ввода символического обозначения команд и данных) и «Комментарий» (для ввода описания выполняемой командой операции или данного).

Отладка программы решения задачи производится с помощью экранной формы исследования ПР-Ф в режиме выполнения программы по командам. При этом биты vm в БППД на форме ввода ПР-В перед выполнением программы устанавливаются в нулевое состояние. Для упрощения отладки на экранной форме исследования ПР-Ф при выполнении команд на выходе БППД отображается символическое обозначение из поля «Мнемоника» формы ввода ПР-В для считываемого содержимого ячейки памяти.

В процессе отладки программы выполняются отдельные команды и необходимые последовательности команд путем занесения в программный счетчик PC начального адреса первой команды, который предварительно вводится с клавиатуры в поле SA. Перед выполнением любой команды также возможно изменение содержимого выбранных регистров в БР (ячеек БППД) с помощью пультового дублера БР (БППД).

После завершения отладки микропрограммы командного цикла и программы решения задачи работа УПР исследуется в режиме выполнения программы. При этом изменяются параметры Microsoft Excel, связанные с вычислением формул: выбираются вычисления в книге «вручную» и включаются итеративные вычисления с предельным числом итераций, превышающим удвоенное максимальное число микрокоманд, необходимых для выполнения программы. В процессе исследования программы могут быть получены результаты решения задачи, подтверждающие корректность выполнения программы по всем ветвям алгоритма.

Заключение

В применяемой функциональной модели процессора с микропрограммируемой архитектурой, кроме базовых функций, необходимых для реализации учебных процессоров, предусмотрены следующие дополнительные возможности:

– наличие на экранных формах, предназначенных для экспериментального исследования и ввода информации, специальных полей, в которых отображаются мнемонические обозначения и пояснения, облегчающие понимание изменений состояний процессора при проведении экспериментальных исследований;

– использование пультовых дублеров регистров и ячеек памяти, позволяющих заносить данные в регистры и ячейки памяти перед выполнением любой микрокоманды (команды) с использованием клавиатуры, что упрощает и ускоряет отладку микропрограмм и программ;

– наличие различных режимов работы учебного процессора, позволяющих выполнять отдельные микрокоманды, команды и всю программу.

Микропрограммная реализация и экспериментальное исследование учебных процессоров осуществляются по индивидуальным заданиям и способствуют более глубокому изучению архитектуры, структуры и рабочего цикла процессора, позволяют разработать простейший учебный процессор, создать и исследовать его действующую модель. При наличии у обучающегося необходимой предварительной теоретической подготовки решение задачи построения процессора в рассмотренной постановке не вызывает больших затруднений и формирует целостное представление о процессоре. Поскольку экспериментальные исследования выполняются в табличном процессоре Microsoft Excel, с которым, как правило, обучающиеся уже знакомы, им не требуется дополнительного времени для изучения программного интерфейса.

Библиографическая ссылка

Страбыкин Д.А. МИКРОПРОГРАММНАЯ РЕАЛИЗАЦИЯ И ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ УЧЕБНОГО ПРОЦЕССОРА В MICROSOFT EXCEL // Научное обозрение. Технические науки. 2023. № 3. С. 21-29;URL: https://science-engineering.ru/en/article/view?id=1438 (дата обращения: 14.05.2026).

DOI: https://doi.org/10.17513/srts.1438

science-review.ru

science-review.ru