Введение

Изучение языков программирования аппаратуры в колледжах имеет ряд важных преимуществ, связанных с развитием технических навыков, подготовкой к будущей профессии и пониманием принципов работы современных цифровых систем [1, 2]. Эти языки являются ключевыми инструментами в области проектирования цифровых устройств, включая программируемые логические интегральные схемы (ПЛИС) [3]. Несмотря на отличие от традиционных языков программирования, они развивают алгоритмическое мышление и умение структурировать задачи, требуют чёткого описания поведения системы, поддерживают моделирование и проверку проектов до их физической реализации. Это способствует развитию у студентов умений анализировать и отлаживать системы на ранних этапах разработки, снижая риск ошибок. Знание этих языков повышает конкурентоспособность выпускников на рынке труда [4], а также может стать отправной точкой для освоения более сложных инструментов или языков высокого уровня для системного проектирования [5].

Наряду с этим все более важным становится понимание принципов работы ПЛИС, получивших широкое применение в промышленности, особенно в сферах телекоммуникаций, аэрокосмической отрасли, потребительской электроники и разработки микросхем [6]. Особое значение понимание этих принципов приобретает в эпоху развития интернета вещей и искусственного интеллекта [7].

Изучение ПЛИС и языков программирования аппаратуры объединяет знания из математики, физики, информатики и инженерии, способствуя комплексному пониманию технологий. При этом работа над реальными проектами (например, создание простых цифровых устройств) мотивирует учащихся и развивает навыки командной работы [8, с. 18].

Таким образом, введение языков программирования ПЛИС в программу колледжей способствует формированию инженерных компетенций, пониманию основ современной электроники и подготовке к будущим профессиональным вызовам. Однако важно учитывать, что эти языки требуют тщательного изучения и практики, а их преподавание должно сопровождаться доступом к соответствующим инструментам.

Цель исследования – разработка и верификация образовательного проекта на примере интерфейса дисплея в составе учебного стенда для обучения студентов технических колледжей основам языков программирования ПЛИС.

Материалы и методы исследования

Аппаратной платформой исследования является учебный стенд SDK-6.1/E производства ООО «ЛМТ» (г. Санкт-Петербург) [9, 10, 11]. Стенд предназначен для изучения основ проектирования современных электронных модулей на базе ПЛИС средней степени интеграции. Наличие в составе стенда ПЛИС Cyclone производства Intel/Altera1 и подсистемы памяти (FLASH, SRAM, EEPROM) позволяет создавать на его основе полнофункциональное вычислительное ядро. Роль буквенно-цифрового знак синтезирующего модуля в стенде выполняет жидкокристаллический (ЖК) дисплей модели WH1602B-YGK-CP.

Дисплей имеет внутреннюю память для определения матрицы символов, а также стандартного множества символов.

Программными средствами исследования являются среда проектирования Quartus II компании Intel/Altera2 и язык описания аппаратуры Verilog [12, 13].

Исходными материалами исследования являются также руководство пользователя стенда SDK-6.1/E, спецификации ЖК дисплея WH1602B YGK CP3 и контроллера4.

Анализ архитектуры стенда и протокола обмена данными между ПЛИС и ЖК дисплеем определил необходимость исследования особенностей 4-разрядного режима работы дисплея. Одной из проблем, возникающих в процессе отладки и моделирования схем на стенде SDK-6.1/E [14], является построение интерфейса управления ЖК дисплеем, выводы которого соединены с ПЛИС в соответствии с таблицей.

Младшие выводы данных (DB0 – DB3) дисплея не используются, т. к. в стенде реализуется 4-разрядный интерфейс.

На основе результатов анализа проведено проектирование интерфейса: разработаны схема драйвера дисплея и модуль ее тестирования на языке Verilog, реализованы алгоритмы инициализации и передачи данных.

Для моделирования и отладки драйвера и тестера дисплея использовалась среда Quartus II, в которой проводилась проверка временных диаграмм и верификация преобразования 8-битных данных в две 4-битные посылки.

Для подтверждения работоспособности предложенного решения была проведена экспериментальная проверка путем загрузки разработанных модулей образовательного проекта в ПЛИС стенда SDK-6.1/E.

Результаты исследования и их обсуждение

При выполнении образовательного проекта разработан интерфейс управления дисплеем для учебного стенда SDK 6.1/E на базе ПЛИС Cyclone компании Intel/Altera, реализующий 4 разрядный режим обмена данными.

Это позволило эффективно использовать ограниченные ресурсы стенда при сохранении функциональности отображения информации.

Соединения ЖК дисплея и ПЛИС в стенде SDK-6.1/E

|

Функции дисплея |

Вывод дисплея |

Вывод ПЛИС |

|

RS (выбор регистра) |

4 |

132 |

|

R/W (чтение/запись) |

5 |

130 |

|

E (сигнал разрешения) |

6 |

131 |

|

DB4 (данные) |

11 |

124 |

|

DB5 (данные) |

12 |

125 |

|

DB6 (данные) |

13 |

128 |

|

DB7 (данные) |

14 |

129 |

Примечание: составлена автором на основе полученных данных в ходе исследования.

Разработанный интерфейс устраняет одну из проблем отладки схем на стенде – сложность интеграции дисплея с ПЛИС. Использование 4 разрядного режима оптимизирует количество задействованных выводов ПЛИС (всего 7 сигналов вместо 11 при 8 разрядном интерфейсе).

В результате анализа спецификации ЖК дисплея WH1602B YGK CP определены ключевые этапы передачи данных между ПЛИС и дисплеем.

До того, как ЖК дисплей сможет отобразить записанную в него информацию, он должен быть проинициализирован и запрограммирован. Программирование выполняется путем удержания входов RS и R/W в низком состоянии, подачи команд на входы с DB7 по DB0 и выдачи строб-сигнала E.

После инициализации ЖК дисплея в него записываются 8-битные данные кода ASCII путем установки входов RS и R/W в 1 и 0 соответственно, помещения данных кода ASCII на входы DB7 – DB0, формирования сигнала E и предоставления порядка 40 микросекунд времени для выполнения операции. Каждый раз, когда байт данных записывается в ЖК дисплей, курсор перемещается на одну позицию вправо.

При организации 4-разрядного интерфейса байт передается в 2 посылки, старшим битом вперёд. В спецификации дисплея первая посылка обозначается D7 (старшая тетрада), а вторая – D3 (младшая тетрада). Перед следующей посылкой проверяется наличие флага занятости. Если он отсутствует, то процесс передачи можно продолжить, в противном случае придется подождать, пока контроллер, управляющий дисплеем, завершит предыдущие операции. Для упрощения инициализации чтение флага занятости может быть заменено задержкой. В соответствии с этим для передачи байта в 2 посылки необходимо выполнить следующие шаги:

• убедиться, что управляющий контроллер свободен,

• установить RS в 0 (команда) или 1 (данные), в зависимости оттого, что передается,

• R/W установить в 0,

• установить строб-сигнал E в 1,

• поместить на шину данных (DB4 – DB7) старшую тетраду D7 передаваемого байта,

• выполнить задержку 2мкс,

• сбросить строб-сигнал Е в 0,

• выполнить задержку 1мкс,

• установить строб-сигнал E в 1,

• поместить на шину данных (DB4 – DB7) младшую тетраду D3 передаваемого байта,

• выполнить задержку 2мкс,

• сбросить строб-сигнал Е в 0.

Схема интерфейса управления дисплеем реализована на языке программирования аппаратуры Verilog [15]. Оформленный в виде модуля драйвера LCD_drv_8_to_4 в пакете Quartus II, интерфейс осуществляет инициализацию дисплея и преобразование 8-битных данных в последовательность полубайтов, позволяющую подключиться к дисплею по 4-разрядной шине. Функционирование схемы поясняют комментарии в коде описания модуля, что важно при выполнении образовательного проекта на Verilog.

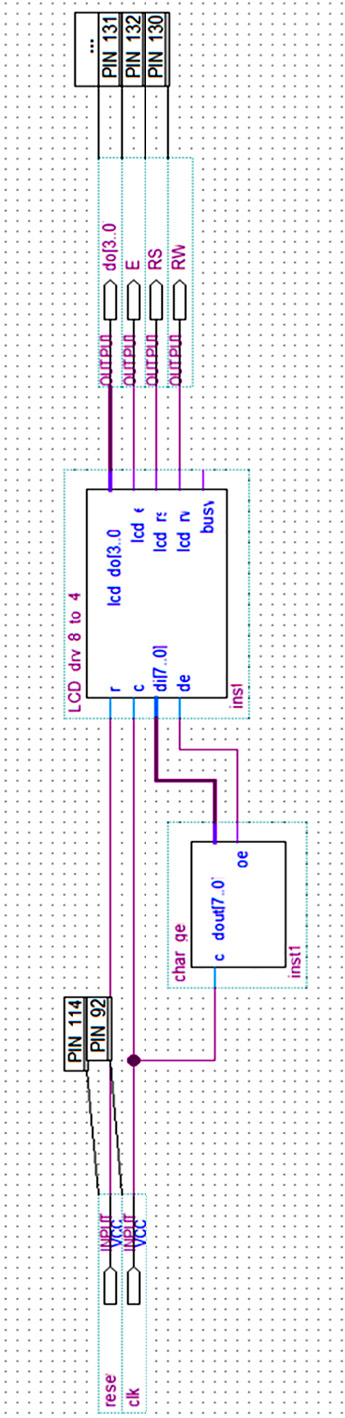

Общая схема тестирования драйвера ЖК дисплея применительно к ПЛИС стенда SDK-6.1/E показана на рисунке. Генерируемые тестером char_gen символы выводятся с помощью драйвера LCD_drv_8_to_4 на дисплей. Управляющий сигнал схемы reset формируется на плате стенда переключателем SW5, а сигналы тактовой последовательности clk задаются внутренней системой синхронизации стенда.

module LCD_drv_8_to_4 (

// системные сигналы

input r, // сброс системы

input c, // синхронизация

// входные порты

input [7:0] di, // 8-битные ASCII

input de,

// выходные порты LCD 4-bit

output [3:0] lcd_do, // LCD 4-битные данные

output lcd_e, // LCD E строб

output lcd_rs, // LCD R/S: 0 – команда, 1 – данные

output lcd_rw, // LCD R/W: 0 – запись, 1 – чтение

output busy );

`define ms_clk_val 50000 // такты на 1 мс; 50000 – для частоты @ 50 MГц, 500 – для отладки/моделирования

`define lcd_E_duration 30 // 600 нс @ 50 MГц (600 * 50 / 1000)

reg [7:0] di_r;

reg [2:0] state; // рабочее состояние

reg [3:0] i_state; // состояние инициализации ЖК дисплея

reg [4:0] cnt;

reg [15:0] init_seq [10:0]; // начальная последовательность

reg [15:0] cnt_1ms;

reg [5:0] delay_ms;

wire next_stt_en;

wire [2:0] next_stt_val;

wire cnt_en;

wire de4, de8; // 1 или 2 срезающих строба

wire is_init = i_state != 10; // инициализация в процессе

wire de_i; // data enable internal strobe

wire in_transmitt = (state != 0);

wire [15:0] d_init;

wire next_init_en;

wire cnt_1ms_zero = cnt_1ms == 0;

wire cnt_1ms_en = 1;

wire delay_ms_zero = delay_ms == 0;

assign d_init = init_seq[i_state];

assign busy = in_transmitt | is_init;

assign lcd_do = ((state == 1) | (state == 2)) ? di_r[7:4] : di_r[3:0];

assign next_stt_en = in_transmitt ? cnt == 0 : de_i;

assign cnt_en = in_transmitt;

assign lcd_e = ((state == 1) | (state == 3));

assign lcd_rs = !is_init;

assign lcd_rw = 0;

assign next_stt_val = (state == 4) ? 0 : (state + 1);

assign next_init_en = is_init & !in_transmitt & delay_ms_zero;

assign de4 = !d_init[8] & next_init_en;

assign de8 = d_init[8] & next_init_en;

assign de_i = (de & !busy) | (d_init[9] & (de8 | de4));

task reset_reg;

begin

cnt <= 0;

state <= 0;

di_r <= 0;

i_state <= 0;

delay_ms <= 0;

cnt_1ms <= 0;

end

endtask

initial begin

// инициализация всех регистров

reset_reg();

init_seq[0] <= 16'b_110010_0_0_00000000; // ожидание 50 мс после включения

init_seq[1] <= 16'b_000101_1_0_00000011; // установить 8-битный режим

init_seq[2] <= 16'b_000101_1_0_00000011; // установить 8-битный режим

init_seq[3] <= 16'b_000101_1_0_00000011; // установить 8-битный режим

init_seq[4] <= 16'b_000101_1_0_00000010; // установить 4-битный режим

init_seq[5] <= 16'b_000001_1_1_00101000; // 28 2 строки, шрифт char

init_seq[6] <= 16'b_000001_1_1_00001100; // 0С дисплей включить

init_seq[7] <= 16'b_000011_1_1_00000001; // 01 очистка дисплея

init_seq[8] <= 16'b_000001_1_1_10000000; // 80 курсор влево/вверх по экрану

init_seq[9] <= 16'b_000000_0_0_00000000; // конечное состояние – без инициализации

init_seq[10] <= 16'b_000000_0_0_00000000; // конечное состояние – без инициализации

end

always@(posedge c) begin

if(r) begin

reset_reg();

end else begin

if(next_stt_en) begin

case(state)

0: if(de_i) state <= de4 ? 3 : 1;

4: state <= 0;

default: state <= state + 1;

endcase

end

if(next_init_en) begin

i_state <= i_state + 1;

delay_ms <= d_init[15:10];

end else begin

delay_ms <= delay_ms – cnt_1ms_zero;

end

cnt_1ms <= (next_init_en | cnt_1ms_zero) ? `ms_clk_val : cnt_1ms – !delay_ms_zero; // счетчик на 1 мс

if(de_i) begin

di_r <= is_init ? d_init[7:0] : di;

cnt <= `lcd_E_duration;

end else begin

cnt <= cnt – cnt_en;

end

end

end

endmodule

Для тестирования драйвера дисплея на языке Verilog создан также модуль char_gen, генерирующий 8 разрядные коды символов ASCII.

module char_gen (

// системные сигналы

input c, // синхронизация

// входные данные

output [7:0] dout, // 8-битный ASCII

output oe

);

reg [7:0] d_r;

reg [23:0] cnt;

wire inc = cnt == 0;

assign oe = inc;

assign dout = d_r;

initial begin

cnt <= 0;

d_r <= 48;

end

always@(posedge c) begin

cnt <= cnt + 1;

if(inc) begin

d_r <= (d_r == 122) ? 48 : d_r + 1;

end

end

endmodule

Схема тестирования драйвера ЖК дисплея для стенда SDK-6.1/E Примечание: составлена автором по результатам данного исследования

Результаты тестирования подтверждают корректную работу 4-разрядного интерфейса и эффективность архитектуры модуля драйвера в части ее универсальности (подходит для дисплеев на базе контроллера HD44780) и масштабируемости (возможность адаптации под другие разрешения ЖК дисплеев).

Практическая значимость исследования заключается в том, что разработанное решение упрощает процесс отладки и моделирования схем на учебном стенде, обеспечивает наглядную обратную связь через дисплей при изучении программирования ПЛИС, а также может быть использовано в лабораторных работах по цифровой схемотехнике и проектированию встраиваемых систем.

Заключение

В ходе проведенного исследования решена задача разработки и верификации образовательного проекта для обучения студентов технических колледжей основам языков программирования ПЛИС.

Исследование проводилось на примере решения проблемы интеграции ЖК дисплея модели WH1602B YGK CP со стендом SDK 6.1/E. В результате обоснована целесообразность применения 4-разрядного режима обмена данными, позволяющего оптимизировать использование выводов ПЛИС.

Разработан модуль драйвера ЖК дисплея на языке Verilog, который выполняет инициализацию дисплея согласно требованиям контроллера HD44780, преобразует 8-битные данные в последовательность полубайтов для передачи по 4-разрядной шине, управляет основными сигналами дисплея в соответствии с протоколом обмена.

Создан тестовый модуль char_gen, генерирующий 8-разрядные коды символов ASCII для проверки работоспособности интерфейса.

Экспериментально подтверждена корректность функционирования разработанного решения.

Результаты работы представляют интерес для студентов, изучающих проектирование на ПЛИС, преподавателей, разрабатывающих лабораторные работы и инженеров, работающих с интерфейсами ЖК дисплеев.

[1]. Cyclone FPGA Family [Электронный ресурс]. Режим доступа: https://www.chipfind.ru/datasheet/pdf/ altera/ep1c6.pdf (дата обращения 22.11.2025).

[2]2 Quartus II Web Edition (Win) [Электронный ресурс]. Режим доступа: https://soltau.ru/index. php/plis/item/360-install-quartus/ (дата обращения 22.11.2025).

[3] LCD 1602B Winstar [Электронный ресурс]. Режим доступа: https://cxem.net/mc/mc89.php/ (дата обращения: 22.11.2025).

[4] Подключение и использование дисплея на базе HD44780 [Электронный ресурс]. Режим доступа: https://microtechnics.ru/podklyuchenie-i-rabota-s-displeem-wh1602/ (дата обращения: 22.11.2025).

Конфликт интересов

Библиографическая ссылка

Болдырев А.В. ИНТЕРФЕЙС ДИСПЛЕЯ ДЛЯ УЧЕБНОГО СТЕНДА НА ОСНОВЕ ПРОГРАММИРУЕМОЙ ЛОГИЧЕСКОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ // Научное обозрение. Технические науки. 2025. № 5. С. 12-18;URL: https://science-engineering.ru/ru/article/view?id=1521 (дата обращения: 14.05.2026).

DOI: https://doi.org/10.17513/srts.1521

science-review.ru

science-review.ru